半導體產業長久以來依賴平面縮小技術來提升性能,但這一方法正逐漸逼近物理極限。面對人工智能應用需求的迅猛增長,英特爾、臺積電和三星等半導體巨頭正加速研發創新解決方案,以期滿足下一代計算設備的需求。其中,3D IC技術已成為這些大廠戰略布局的關鍵一環。

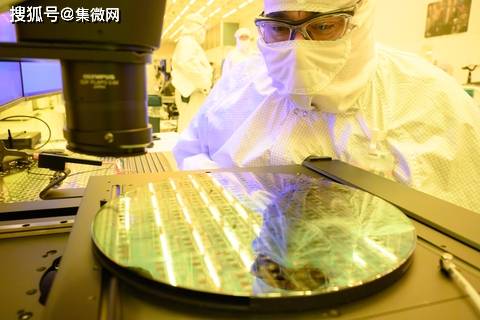

近年來,AI大模型的興起為3D IC技術的快速發展提供了前所未有的契機。3D IC通過垂直堆疊芯片并利用硅通孔(TSV)技術,實現了電子元件的高密度三維集成,與2.5D封裝、Chiplet、扇出型封裝等先進封裝技術一道,成為后摩爾時代提升芯片性能的重要手段。相較于其他技術,3D IC更側重于高性能計算場景,而其他技術則更注重靈活性與成本效益的平衡。

各大半導體廠商早已涉足3D IC技術的研發,但AI大模型的蓬勃發展無疑為這一領域注入了新的活力。臺積電高級副總裁張曉強指出:“為了為客戶提供完整的產品級解決方案,晶體管技術和先進封裝集成必須并行發展。3D架構技術組合對我們來說已變得至關重要。”

英特爾代工業務的高級副總裁Kevin O’Buckley同樣強調了3D IC技術的重要性:“隨著內核數量的增加和計算性能的不斷提升,滿足數據處理需求成為首要任務。3D技術就是一個很好的例子,我們可以利用芯片面積的大部分來放置SRAM,而不必犧牲用于計算的芯片面積。”

盡管3D IC技術顯著縮短了元件間的物理距離,提高了芯片性能并降低了功耗,但這一方法也帶來了更為復雜的子系統需求,在制造工藝、材料科學和設計方法上都提出了新的挑戰。TSV作為3D堆疊的關鍵技術之一,其工藝直接影響互連密度與良率,需要不斷突破更高的深寬比極限。

在制造工藝方面,更先進的等離子刻蝕技術不斷涌現,能夠實現更高的深寬比和更精確的孔形狀控制。在材料方面,除了傳統的銅材料外,新的低電阻、高可靠性導電材料如合金材料和碳納米管復合材料等正在研發中,有望進一步降低信號傳輸損耗。芯片對芯片鍵合技術也至關重要,當前的研究重點集中在提高鍵合精度、速度與可靠性上。

臺積電在3D IC領域形成了以SoIC為核心的技術體系,結合CoWoS和硅光子技術,覆蓋了從邏輯堆疊到異構集成的全鏈條。作為SoIC的首發客戶,AMD通過SoIC與CoWoS結合,實現了帶寬超過5TB/s的AI芯片。臺積電正在開發SoIC 2.0技術,目標將互連節距從當前的9μm縮小至5μm,并引入背面供電技術以提升電源效率和散熱能力。

英特爾則以Foveros為核心技術,結合EMIB和PowerVia技術,形成了覆蓋邏輯堆疊到異構集成的完整技術體系。Foveros通過混合鍵合和TSV技術實現芯片垂直堆疊,支持高密度集成。英特爾正開發Foveros 2.0技術,目標同樣是將互連節距縮小至5μm,并引入背面供電技術。英特爾還在積極開發光連接技術以增強3D IC產品的性能。

三星則以X-Cube為核心技術,在3D IC領域實現了從邏輯堆疊到異構集成的覆蓋。X-Cube通過硅通孔和混合鍵合技術實現芯片垂直堆疊。在熱管理技術方面,三星正在開發微流體冷卻技術,通過在芯片內部嵌入微米級冷卻通道,將散熱效率較傳統風冷提升3倍。三星還在開發光學I/O技術,并計劃將3D IC與下一代制程技術結合,以實現更好的協同效果。